★北京廣利核系統工程有限公司程康,李明鋼

關鍵詞:FPGA;點對點通信;安全級DCS

反應堆保護系統(RPS)作為核電安全級離散式控制系統(DCS)的組成部分,是公認的核電站最重要的安全保障系統,其作用為運行參數達到核安全保護屏障閾值時,緊急停閉反應堆,可以避免核安全事故發生。由于對停堆響應的處理涉及到核電站人員、設備和環境的安全,因此,安全級DCS系統指標對停堆響應時間有著非常嚴格的要求。無論是美國核管會標準評審大綱(NUREG-0800)還是環保部的相關標準(HAD102/16)都對停堆響應時間做出了指導性的說明,停堆響應時間通常應小于0.2s[1][2]。因此,如何減小停堆響應時間,是安全級DCS系統設計中必須要考慮的一個重要因素。

在安全級DCS系統中,停堆響應時間是指從傳感器采集到信號到反應堆保護系統輸出信號再到停堆用電路器所需要的時間,其經過模擬量輸入(AI)、I/O總線處理、點對點網絡通信、主處理器中央處理器(CPU)運算、數字量輸出(DO)等過程。目前,絕大多數研究機構和DCS生產廠商通過優化AI、DO模塊選型、I/O總線端口、CPU應用程序算法等方式減少停堆響應時間[3],但是鮮有通過提高網絡通信的效率來優化停堆響應時間的研究。本研究提出了一種利用可靠性高、速度快、并行處理等優勢的FPGA技術來改進當前通信系統,極大地提高了多通道、大數據容量的點對點通信處理效率,從而對停堆響應時間進行了優化。本文首先介紹了數字化反應堆保護系統的架構及停堆響應時間的計算方法;其次,進一步分析了影響停堆響應時間的因素并且提出了通過點對點通信優化停堆響應時間的可能性;最后,利用FPGA技術優化實現點對點通信并且進行了實驗驗證,證明了此方法對優化保護系統停堆響應時間有著積極貢獻。

1 反應堆保護系統的停堆響應時間

1.1 數字化反應堆保護系統架構

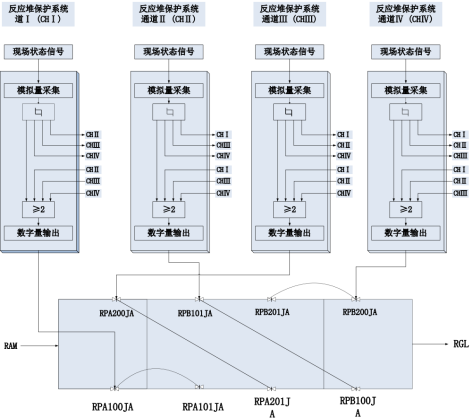

一個典型的數字化反應堆保護系統如圖1所示,從最高級別的安全性考慮,反應堆保護系統采用4通道(CH I、CH II、CH III、CH IV)冗余設計,每個通道相對于其他通道獨立工作且均對應一組測量過程參數傳感器(如溫度、流量、液位、壓力等),在每個通道上進行閾值比較,得出一個“是否超限”的結果,并將此結果發送到其他的通道。每個通道對本通道的閾值比較結果和其他三個通道的閾值比較結果進行“四取二”的邏輯表決,并將結果輸出至該通道斷路器的失電停堆線圈[4]。

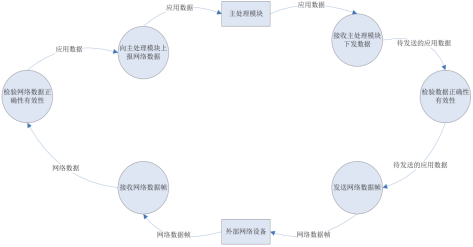

圖1 反應堆保護系統示意圖

1.2 反應堆保護系統信號處理過程

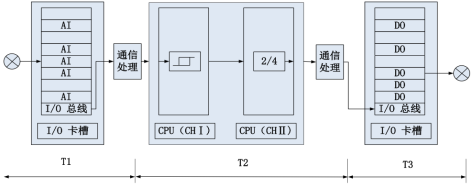

反應堆保護系統信號處理過程如圖2所示,在DCS系統中,AI模塊通過傳感器采集現場的工況信號,經過總線管理模塊后,信號被送至CPU模塊,CPU模塊進行運算處理后將輸出結果通過點對點通信模塊,并且在接收到其他通道通過點對點通信傳來的信息后進行再次處理。最后,通過總線管理模塊將CPU處理后的結果發給DO模塊,最后由DO實現輸出[4]。

圖2 反應堆保護系統信號處理示意圖

1.3 停堆響應時間的計算

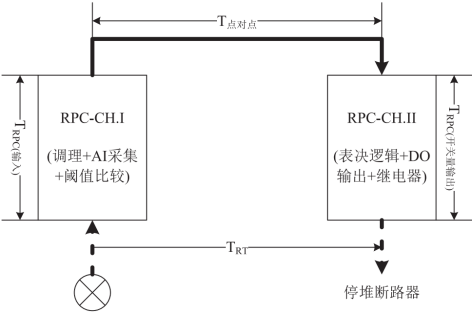

圖3 反應堆保護系統響應時間的計算

根據上述介紹,停堆響應時間的計算可以分為三部分,如圖3所示,系統響應時間TRT為TRT=TRPC(輸入1)+T點對點+TRPC(開關量輸入)。

1.4 停堆響應時間分析

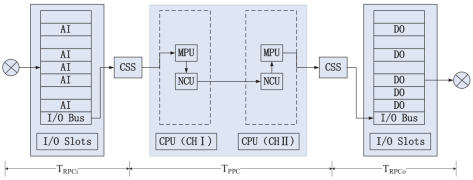

以中國首套擁有自主知識產權的核電安全級DCS和睦系統FirmSys為例,其組成部分與計算,如圖4所示[5]。

圖4 典型反應堆保護系統響應時間計算

在典型的FirmSys系統應用的實例中,主處理模塊周期(tMPU)、I/O通信模塊周期(tSCU)、網絡通信模塊周期(tNCU)和I/O周期(tIO)通常分別設置為15ms、8ms和8ms。因此,按照上述算法,停堆響應時間計算如下:

TRT=TRPCi+1.7TMPU1+2TNCU1+TTrans+1.7TMPU2+2TNCU2+TRPCo

=32+1.7×15+2×8+1.7×15+2×8+32=149(ms)

2 點對點通信對停堆響應時間的影響

2.1 對停堆響應時間影響分析

根據前一章節的描述,我們知道影響停堆響應時間的主要因素為CPU中各模塊的處理時間。CPU模塊所承擔的功能比較復雜,需要從接收AI模塊的信號、進行閾值比較、將比較結果通過點對點通信發送到其他通道、接收其他通道通過點對點通信傳送的數據,到再次進行閾值比較、產生DO模塊輸出信號。換句話說,CPU模塊的處理可以劃分為三個具體的模塊:主控制器模塊、IO數據與總線處理模塊、點對點通信模塊。因此,如果對上述的三個具體模塊進行優化,便可以減小停堆響應時間以提高保護系統的效率。由于在其他研究中對主控制器和IO數據與總線處理部分的研究已經較為成熟,在本研究中我們僅討論目前研究較少的點對點通信模塊部分的優化。

2.2 點對點通信的處理機制

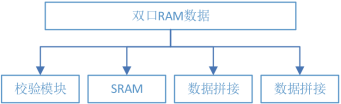

點對點通信模塊為控制站的主處理模塊提供網絡數據的收發,實現框圖如圖5所示。在發送時,主處理模塊將待發送的數據放置在雙口RAM中,點對點通信模塊讀取到雙口RAM的信息后進行數據有效性校驗,通過校驗后的數據通過網卡發出;在接收時,點對點通信模塊通過網卡接收到信息后進行數據有效性校驗,通過校驗后將數據存入到雙口RAM中待主處理模塊讀取。

圖5 點對點通信的數據處理流程

同時,為了核電站的安全性考慮,網絡通信模塊除了與主處理模塊通過雙口RAM交換數據和與其他站點的網絡設備通信模塊進行通信外,根據CEI/IEC60880等規范,它還要實現模塊自診斷、狀態顯示接口、熱備冗余處理、周期性維護等功能[6]。

2.3 點對點通信對停堆響應時間的影響

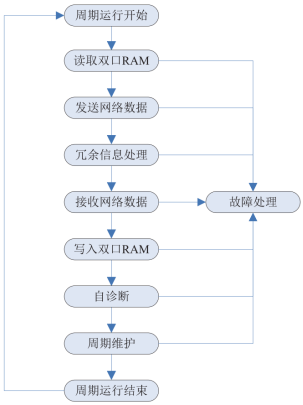

圖6 點對點通信模塊流程圖

基于微處理器的特點,點對點通信模塊各項功能是周期運行的,每一個微處理器在執行周期中所執行的任務如圖6所示,每一項子任務均按順序執行,因此網絡通信模塊的最小執行周期為每項子任務的周期之和。

3 利用FPGA技術優化實現站間點對點通信

在原來微處理器的方案基礎上,對點對點通信模塊做出最小的改動,使用FPGA+雙口RAM的解決方案,可以極大地改善點對點通信的處理周期。

3.1 任務的并行處理

由于FPGA的并行處理能力[7],每一個子任務在FPGA中均可以同時執行。基于FPGA架構的點對點通信模塊的處理框圖如圖7所示。

圖7 基于FPGA技術的點對點通信模塊流程圖

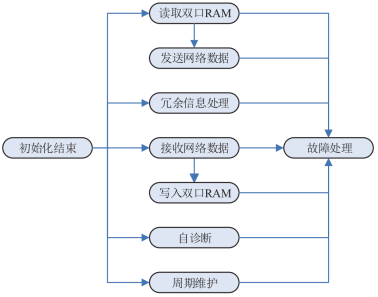

3.2 對網絡數據收發的優化

對于微處理器的從網絡端口1到端口6輪詢的數據收發模式,FPGA的并行處理能力允許系統同時對6個端口的數據進行發送,并且隨時對任一端口的網絡進行接收并且緩存,極大地提高了網絡數據收發的執行速度,縮短了6個端口網絡的收發總體時間。

圖8 點對點通信網絡收發功能框圖

基于FPGA的6端口的點對點網絡通信模塊的網絡數據收發功能框圖如圖8所示。由于雙口RAM不能對同一個地址進行操作,在FPGA中利用狀態控制雙口RAM的讀寫順序,可以避免同時對同一地址的雙口RAM進行操作。

在發送網絡數據的處理中,通信模塊從主處理模塊讀取到待發送數據之后同步進行位寬轉換(32-bit到8-bit)后存入到相應的SRAM中,數據讀取完成并且通過校驗后,會通過網卡立即將6個端口的網絡數據同步發出。

在接收網絡數據的處理中,當檢測到某個或多個網卡有數據接收后,FPGA邏輯會立即對數據進行處理,并存儲到相應的SRAM中,同時進行數據有效性校驗,如果不通過則立即報錯。在系統執行寫雙口RAM操作時,將數據進行位寬轉換(8-bit到32-bit)后存入到相應的雙口RAM中。

因此,在發送數據時,由于FPGA處理可以完成數據有效性校驗、將數據存儲到SRAM、6個端口同時發送,因此較微處理器的執行方式至少節省了數據存儲器間轉移復制、位寬轉換和5倍同一網卡發送的時間。同理,在接收數據時,FPGA處理的方式節省了5倍SRAM復制、存儲期間數據復制和位寬轉換的時間。

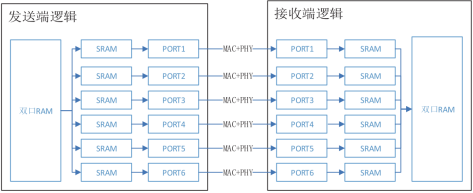

3.3 對雙口RAM處理的優化

圖9 從雙口RAM讀取數據的并行處理FPGA

對主處理模塊交互的雙口RAM的處理如圖9所示,FPGA在讀取雙口RAM中的數據的同時,還進行數據緩存、數據拼接、數據校驗和數據狀態解析等處理。

在讀取雙口RAM數據時,FPGA直接輸出信號訪問雙口RAM的相關引腳,并直接從雙口RAM獲取數據到FPGA內部寄存器,得到的數據同時讀取到SRAM、相關狀態寄存器和數據有效性校驗模塊中,相當于完成了微處理器的三個順序執行任務的工作量。

3.4 基于FPGA實現點對點通信方案的測試

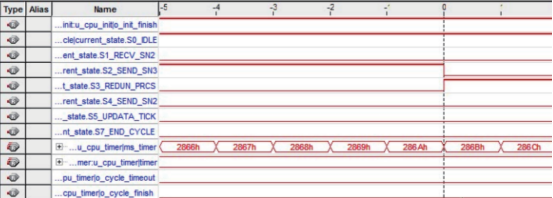

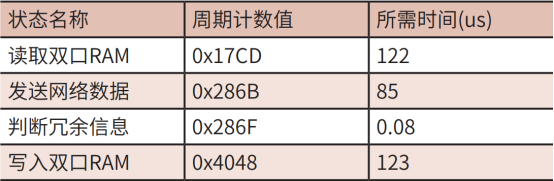

在線邏輯分析儀的使用,如Altera的SignalTap或Xilinx公司的ChipScope對FPGA內部的信號進行抓取,為我們提供了測試基于FPGA的點對點通信模塊的手段[8]。在周期計數器中加入測試點,測試每一個狀態完成后的周期計數器時間,就可以測出通信模塊周期運行時每個狀態所需要的時間,如圖10所示。在狀態機發送網絡數據執行完成后,SingnalTap抓取周期計數器的值為0x286A,時鐘周期為50M,因此狀態機執行讀取SN2數據和發送網絡數據所用的時間為206.92us。表1中列舉了經過換算后的每一個狀態所需要的時間。

圖10 SingnalTap抓取發送網絡數據后周期計數器的值

表1 狀態機各狀態需時間

將接收網絡等待時間設為500us,由表1數據可以計算出網絡接收數據所需要的時間大約為122+85+0.08+123+500=830us,粗略記為1ms。將此數據代入計算公式,重新計算系統響應時間約為:

TRT=TRPCi+1.7TMPU1+TPPC+1.7TMPU2+2TNCU2+TRPCo

=32+1.7×15+0.8+1.7×15+32=117.8(ms)

由此可知,采用FPGA技術點對點通信在原系統中可使響應時間縮短31.2ms。

4 結論

本文分析了基于FPGA技術點對點通信對核電安全級DCS停堆保護響應時間的影響,提出了設計和解決方案,進行了理論計算,并利用在線邏輯分析儀對方案進行了測試和驗證。結果表明,由于FPGA具有速度快、并行執行等特點,利用FPGA技術實現點對點通信,可以極大優化停堆保護的響應時間。

FPGA技術的應用是未來核電安全級通信發展的方向,目前對于FPGA技術在核電安全級DCS設備上并沒有得到廣泛的應用。在以后的研發過程中,利用FGPA實現安全級DCS的其他設備和功能是未來核安全級保護系統的研究方向。

作者簡介:

程 康(1983-),男,高級工程師,碩士,現就職于北京廣利核系統工程有限公司,主要從事核安全級儀控系統設計方面的研究。

李明鋼(1977-),男,河南平頂山人,高級工程師,學士,現任北京廣利核系統工程有限公司副總經理,主要從事核電儀控系統設計制造生產管理相關工作。

參考文獻:

[1] NUREG-0800,Guidance on Digital Computer Real-Time Performance[S].

[2] HAD102/16, 核動力廠基于計算機的安全重要系統軟件[S].

[3] 鄭偉智, 李相建, 朱毅明. 核電站數字化反應堆保護系統停堆響應時間分析[J]. 自動化博覽, 2010, 8 : 74 - 76.

[4] 汪績寧, 周愛平, 郄永學, 等. 核電廠反應堆保護系統緊急停堆響應時間分析及測試[J]. 核動力工程, 2012, 33 (2) : 5 - 10.

[5] 張冬冬, 蒙海軍. 紅沿河核電站安全級DCS 控制系統[J]. 電力建設, 2009, 6 : 66 - 68.

[6] CEI/IEC 60880, Nuclear power plants-Instrumentation and control systems important to safety-Software aspects for computer-Based systems performing category a functions[S].

[7] McNelles P, Lu L. A review of the current state of FPGA systems in nuclear instrumentation and control[C]. //AMSE, Proceedings of the 2013 21st International Conference on Nuclear Engineering, Chengdu : ICONE21.

[8] Intel. Intel Quartus Prime Pro Edition User Guide[R]. USA : Intel Corporation. 2018.

摘自《自動化博覽》2023年10月刊

案例頻道

案例頻道